过去三十年,碳化硅功率半导体行业取得了长足的进步,但在降低缺陷方面依然面临着重大挑战。其主要问题是——碳化硅与栅氧化层之间的界面处存在着大量的缺陷。在NMOS中, 反型层中产生的电子被高密度的界面陷阱等缺陷捕获,导致沟道内有效载流子数目大幅减少。此外,部分陷阱在俘获电子之后会变成带电中心,致使沟道表面的库仑散射效应加剧,沟道迁移率会进一步下降。

半导体材料的电子迁移率是指,电子在单位电场作用下的平均速度,是衡量电子在被电场拉动(或推动)并穿过半导体材料时速度的量度。电子迁移率越高的半导体材料,电阻率越低,通过相同的电流,损耗越小。由于碳化硅材料的电子迁移率比硅和氮化镓都要低,若不采取手段实现该技术难点的突破,SiC MOSFET将面临着因低沟道迁移率导致性能大打折扣的局面。

▲碳化硅材料的电子迁移率不高

为了在晶圆表面形成栅氧化层,器件制造厂商通常会选择热氧化处理工艺。对于传统的硅基MOSFET来说,硅晶圆表面可产出高质量的氧化层。对于碳化硅晶圆,不仅无法通过热氧化获得高质量的氧化层,更为严重的是,SiC与SiO2之间的界面缺陷比Si与SiO2之间高了100多倍。

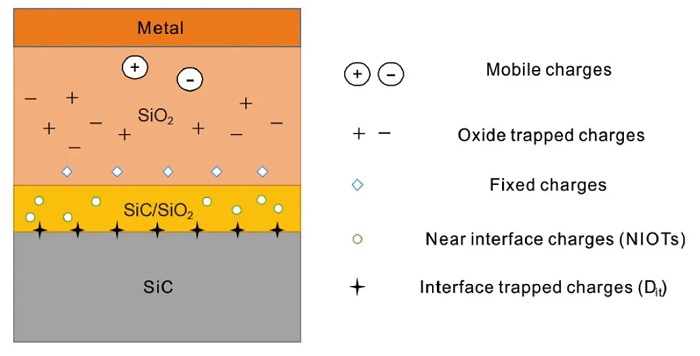

▲碳化硅界面缺陷的主要类型

如上图所示,根据位置分布,通常将SiC/SiO2界面附近的缺陷分为,界面陷阱(Dit)、近界面氧化物陷阱(NIOTs)、固定电荷、氧化层陷阱及移动电荷。其中界面陷阱主要指位于碳化硅表面的陷阱,主要包括由于热氧化产生的含碳副产物缺陷、悬挂键和晶格失配等形成的陷阱。

界面陷阱主要由金属杂质、结构缺陷和氧化诱导等因素引起。界面陷阱会影响电子输运及复合,降低可移动电子浓度,增加界面散射, 导致沟道迁移率下降, 比导通电阻上升。在硅中,氢和氮原子可以有效地消除界面陷阱,但在碳化硅中,氢钝化效果相对较弱,无法显著消除界面陷阱。

一、无碳残留、低缺陷的氧化层

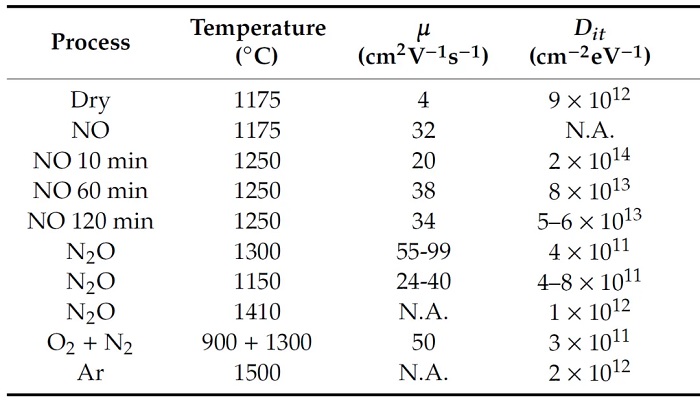

众所周知,退火工艺可以在一定程度上减少界面缺陷,降低界面陷阱密度,进而提升沟道迁移率。特别是在含氮氛围中退火,可以有效地将沟道迁移率提升6~12倍。

但由于退火温度太高(约1300℃),这会导致SiC/SiO2界面出现碳残留。残留的碳主要以下面几种形式存在,如C-Si键、碳空位、硅酸盐和碳化物。鉴于含碳副产物引发的界面缺陷是导致沟道迁移率下降的主要原因,因此业界迫切需要开发一种无碳残留的栅氧化层制作工艺。

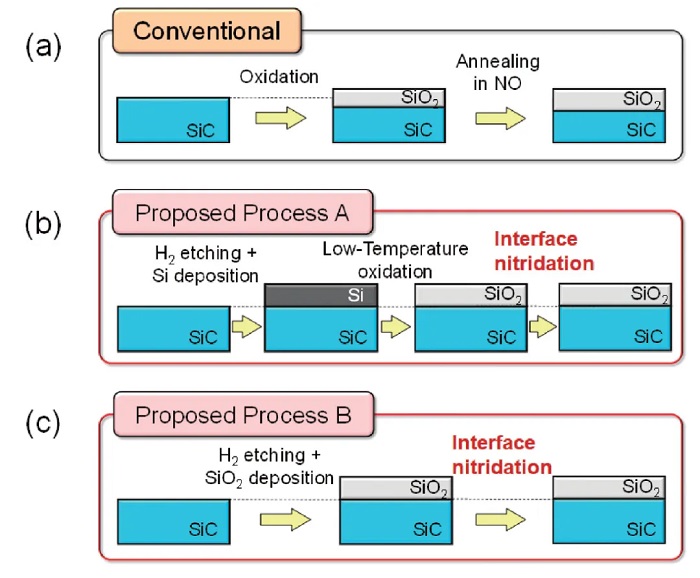

日本京都大学的木本恒畅科研团队,在2022年提出了一项关于制作高质量栅氧化层的工艺。大致流程如下:首先,通过氢刻蚀去除残留在碳化硅晶圆表面的缺陷;其次,分两种方式制作氧化层:一(Process A)是在晶圆表面先沉积一层硅薄膜,然后在750°C低温下进行氧化,可将其转换为SiO2薄膜。由于硅氧化的起始温度为700℃,而碳化硅的氧化起始温度为900℃,因此750℃仅氧化硅而不会氧化碳化硅。二(Process B)是使用化学气相沉积(CVD)方式直接沉积SiO2薄膜。

▲高质量氧化层制作工艺流程

最后,引入氮原子以实现界面的高质量化。传统退火工艺通常使用一氧化氮对界面进行氮化,但碳化硅不可避免地会被一氧化氮中的氧原子氧化,产生新的缺陷。因此,新退火工艺避免使用一氧化氮,而采用在高温氮气氛围中热处理来提高界面质量。最终的评估结果是,Process A可以将界面缺陷密度降低到传统工艺的十分之一,而Process B可以将界面缺陷密度降低到传统工艺的五分之一。

考虑到界面缺陷的大幅降低,以600V或1200V的SiC MOSFET为例,其导通电阻可降低25~35%。换句话说,原来65~75%的芯片尺寸就可以达到相同的额定电流,从而可以将器件成本降低约30%。由于新工艺不采用一氧化氮,相关成本还会进一步下降。因为使用剧毒的一氧化氮不但危险,而且还会增加安装和维护废气处理设备以及检测警报的成本。

二、优质的垂直晶面成膜

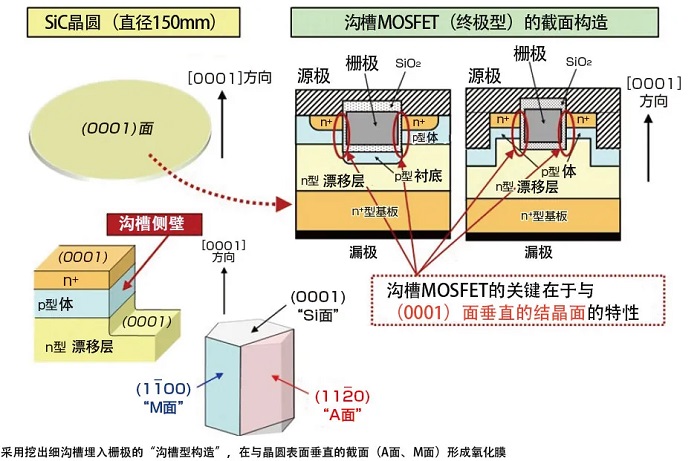

日本京都大学木本教授的科研团队,不仅提出了关于高质量栅氧化层的制作工艺,而且发现在制造沟槽型MOSFET时,选择与硅面(0001)垂直的A面或M面上形成栅氧化层,与传统的硅面成膜的工艺相比,沟道迁移率可以提高约6~7倍。

▲沟槽型MOSFET新的垂直晶面选择

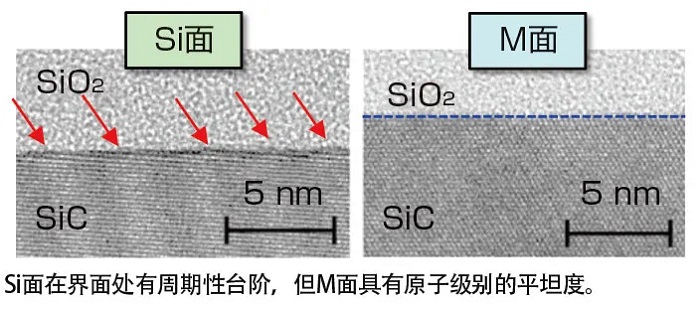

▲不同晶面成膜后粗糙度对比

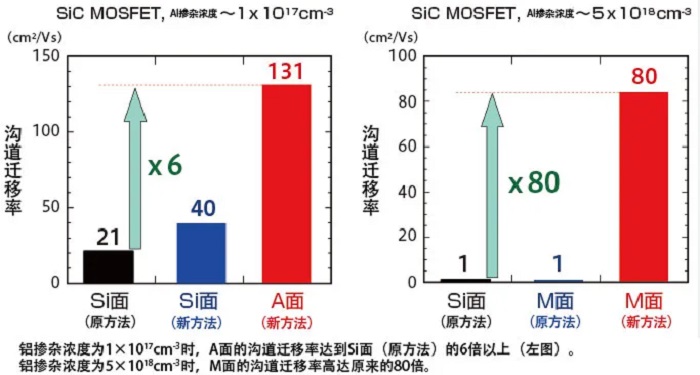

此外,通过掺杂较高浓度的铝形成p阱,并在A面和M面上制造出了沟槽型SiC MOSFET。测量结果表明,相比传统的平面型(Si面),基于A面和M面的新晶面成膜方法将沟道迁移率分别提高到了6倍和80倍。这样一来,不仅器件的可靠性大大提高,而且面积大幅减少,使成本可降低到原来的三分之一左右。

▲不同晶面成膜导致沟道迁移率差异

三、眼前一亮的混合外延层

要知道,3C-SiC MOSFET的沟道迁移率为100~370cm2/V·s,而4H-SiC MOSFET通常为20~40cm2/V·s,沟槽型器件为6~90cm2/V·s。上面提到,京都大学可以将沟道迁移率最高做到131cm2/V·s,但仍比3C-SiC MOSFET低三倍左右。

设想如果能够制造一种混合外延层,既利用3C-SiC材料的高电子迁移率,又利用了4H-SiC材料的高击穿场强。要实现这一目标,则需要开发一种新的外延生长技术,以无缝堆叠两种不同晶型的碳化硅层。

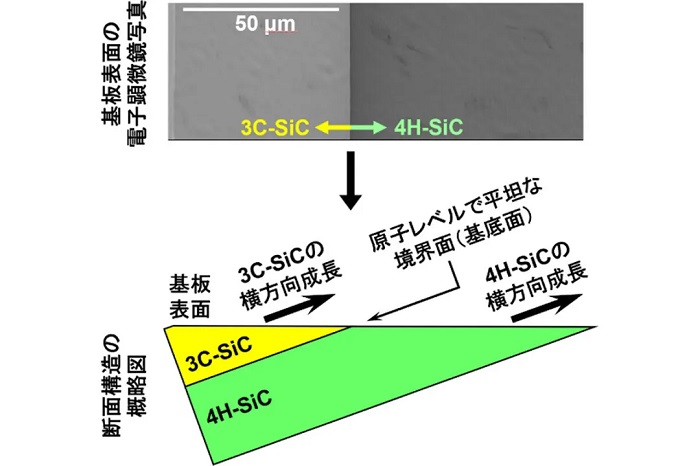

2023年9月,日本东北大学的科研团队发明了一种名为同步横向外延(Simultaneous Lateral Epitaxy,SLE)生长方法。简单来说,就是在4H-SiC的延伸基面上生长3C-SiC层,3C-SiC也沿着4H-SiC基面延伸,这样使得3C-SiC层与4H-SiC层之间的界面非常平坦,完全没有原子偏差。

▲SLE外延层生长法

使用扫描非线性介电常数电镜(SNDM)测量的结果表明,3C-SiC表面的缺陷密度仅为4H-SiC的两百分之一。SLE法大幅降低了界面缺陷密度,预测制作的MOSFET可将损耗降低30%以上。

由于SLE法能够直接在碳化硅外延层表面引入不同的晶体结构,而无需大幅改变现有的SiC MOSFET器件形状或制造工艺,预计该方法可以快速导入现有的器件生产线。

总结

本文介绍了三种碳化硅MOSFET沟道迁移率提升工艺,包括通过工艺创新制作无碳残留、低缺陷氧化层;针对沟槽型器件选择优质垂直晶面成膜;使用SLE生长法制作含高迁移率的3C-SiC混合外延层。

SiC MOSFET器件目前存在两个主要技术难点没有完全突破:低沟道迁移率和高温、高电场下栅氧化层的可靠性。在克服这两个问题后,碳化硅功率半导体行业将迎来爆发式增长。

| 上一篇:叠层母排寄生电感的评估与优化(一) | 下一篇:IGBT器件技术——氢注入场截止技术 |

安徽省合肥市高新区长宁大道789号5号楼