SiC 功率模块串扰机理及解决方案

串扰问题(Cross talk)半桥电路中,SiC MOSFET芯片开关动作引起另一个 SiC MOSFET 芯片开关的栅源极电压波动的问题,分为正向串扰和负向串扰。

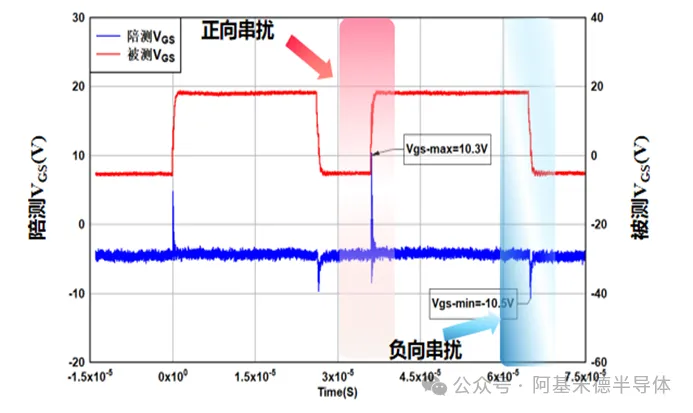

以某款1200 V/14mΩ SiC MOSFET芯片为例,栅极开通控制电压为+18 V,栅极关断电压为-5 V。如图1所示,当半桥电路发生正向串扰时,被测SiC MOSFET(以下简称“被测管”)的栅极电压由-5 V升高至+18 V,被测管开通过程会引起陪测SiC MOSFET (以下简称“被测管”)的栅极电压从-5 V向 0 V方向升高,即正向抬升,若正向抬升超过被测管栅极阈值将导致误开通,造成短路。负向串扰发生在被测管关断的过程,被测管栅极由+18V降低为-5 V,被测管关断过程则引起陪测管栅极电压从-5 V向更低负压方向变化,即负向增大,若负向增大超过陪测管栅极负压耐受极限将会导致栅极击穿,从而造成器件失效。

图1. 串扰典型波形

一、串扰的机理

串扰主要有两个地方产生,一个是由于Crss的充放电产生的电流,另一个是驱动回路中共源极的寄生电感产生的感应电压,两者都会通过驱动回路影响到栅极电压。

1.共源极电感产生的串扰

共源极电感引起的串扰电压,主要是电流变化在电感两端产生感应电压导致的,外接驱动回路阻抗与Cgs串联,驱动回路阻抗越大,Cgs分压越小,所以产生的尖峰也会更小。所以电压尖峰的产生是由于Cgd以及Ls共同导致的结果,且两者产生的电压尖峰与驱动电阻大小呈相反的关系。

2.Crss充放电产生的串扰

(1)正向串扰

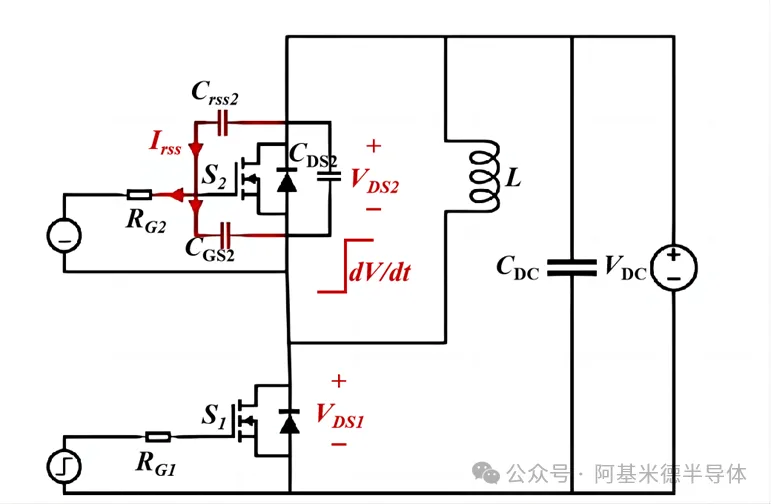

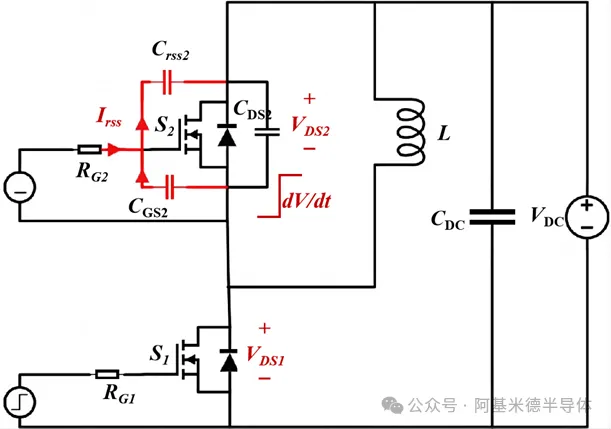

首先分析正向串扰,双脉冲测试的电路图如图2所示,S1和S2分别表示被被测SiC器件和陪测SiC器件。CGS2和Crss2和CDS2分别为S2的栅源极电容、米勒电容、漏源极电容。

图2 正向串扰原理图

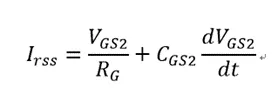

在图2中的半桥电路中,在S2上施加关断驱动信号,当S1未开通时,其体二极管处于续流状态。当S1进行开通时,其端电压VDS1下降,则S2开始承受反向电压,其两端的电压VDS2以dV/dt的速度快速上升。那么dV/dt就会通过S2的Crss2产生位移电流Irss=Crss2*dV/dt,Irss会流入S2的驱动回路,对CGS2充电,并在RG2上产生压降。根据基尔霍夫定律可得:

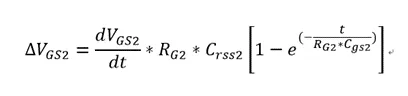

由上式可以得到陪测管串扰电压大小为:

为电压变化率,当电压变化率为正时产生正向串扰电压,当电压变化率为负时产生负向串扰电压。图3中,S1依旧为被测管,此时进行的是关断。此时整个过程与正向串扰原理一样,只是电压和电流的变换方向相反,最终S2的驱动电压VGS被向下拽,出现一个反向的尖峰。

图3负向串扰原理图

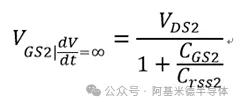

为了发挥SiC MOSFET开关损耗小的性能优势,需要加快开关速度,因而会增大漏源极间的电压变化率,使串扰问题变得更加严重。极限情况下,假设电压变化率无穷大,则串扰电压的极限值为:

根据串扰电压的表达式分析,为了在不影响开关管驱动效果的前提下有效降低栅极串扰电压,选择栅源极寄生电容与栅漏极寄生电容比值较大的开关管尤为重要。这种选择不仅有助于优化电路性能,还能在高频开关环境中保持稳定性。

但是在实际应用中,如果芯片的型号已经确定,仍然可以通过一些电路设计技巧来改善串扰电压问题。具体而言,可以在开关管的栅源极间并联适当的电容,以增加栅源极的等效电容。这种方法能够进一步降低栅极串扰电压,从而提升整体电路的抗干扰能力和可靠性。此外,优化布线布局、使用屏蔽技术以及选择合适的驱动电路也是有效的辅助措施。这些方法可以协同作用,共同抑制栅极串扰电压,确保开关管在各种工况下的稳定运行。

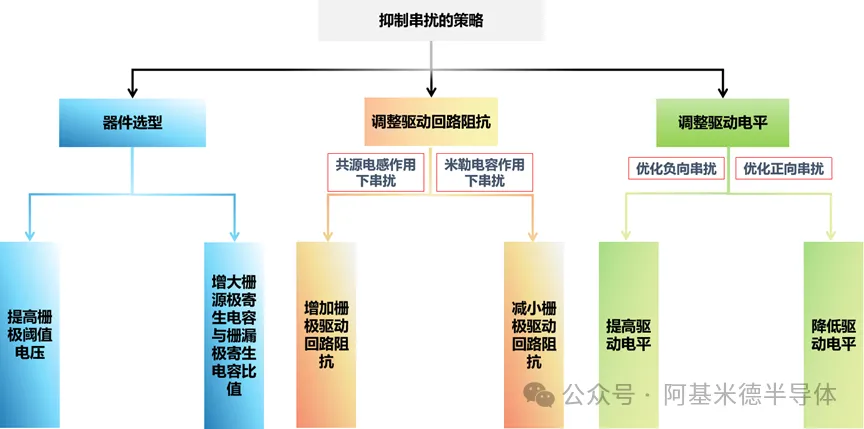

二、串扰的抑制方法

图4 抑制串扰策略

(1)选择合适的功率芯片

选择栅源极寄生电容与栅漏极寄生电容比值较大的功率芯片,有助于减少栅极串扰电压。这种选择可以在设计阶段尽量降低栅极受到的干扰。

(2)调整驱动回路阻抗抑制串扰

从串扰产生机制可知,栅极驱动阻抗和位移电流是造成栅源极电压正向抬升和负向增大的直接因素, 减小栅极驱动阻抗和位移电流,则能抑制串扰引起的栅源极电压变化幅值。增大栅极驱动回路阻抗可以有效抑制共源极电感作用下的串扰,可通过增大栅极驱动电阻或将栅极驱动回路开路的方式增大栅极驱动回路阻抗,进而抑制共源极电感作用下的串扰。减小栅极驱动回路阻抗可以有效抑制米勒电容作用下的串扰,可通过减小栅极驱动电阻或在栅极和源极之间并联大电容的方式来提供低阻回路,减小流经栅源极电容的位移电流,进而抑制米勒电容作用下的串扰。

(3)通过调整驱动电平抑制串扰

在共源极电感作用下的开通串扰和米勒电容作用下的关断串扰,都会引起栅源电压降低,可通过提高栅极驱动电平来抑制串扰下的栅源电压负尖峰。在米勒电容作用下的开通串扰和共源极电感作用下的关断串扰,都会引起栅源电压的升高,可通过降低栅极驱动电平来抑制串扰下的栅源电压正尖峰。如采用有源米勒箝位(Active Miller Clamp,AMC)技术,限制栅源极电压串扰波形幅值。