如果有人跟你说:“嗨,我做的芯片实现了100%自主可控!”等等,你先不急着崇拜(相信)他,请看完此文再说...

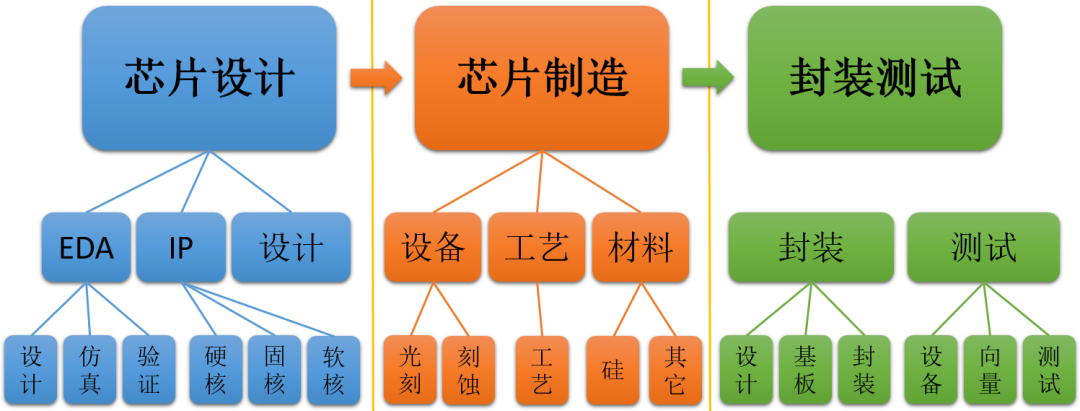

首先,什么叫自主可控,最直观的理解就是当别人“卡脖子”的时候不会被卡住。集成电路产业通常被分为芯片设计、芯片制造、封装测试三大领域,参看下图:

我们逐一进行分析,芯片设计主要从EDA、IP、设计三个方面来分析;芯片制造主要从设备、工艺和材料三个方面来分析;封装测试则从封装设计、产品封装和芯片测试几方面来分析。

01

芯 片 设 计

如何开始一款芯片设计呢?

首先要有工具(EDA),然后借助现有的资源(IP),加上自己的构思和规划就可以开始芯片设计了。这里,我们就从芯片设计工具EDA,知识产权IP,以及集成电路的设计流程来分析芯片设计。

1.1 EDA

EDA(Electronic Design Automation)电子设计自动化,常指代用于电子设计的软件。

曾经有人跟我说:“EDA有啥呀,不就是个工具嘛?”是啊,确实就是个工具,可是没这个工具,你啥也设计不了啊!

现在的大规模集成电路在芝麻粒大小的1平方毫米内可以集成1亿只以上的晶体管,这些晶体管之间的连接网络更是多达数亿个。当今主流的SoC芯片,其晶体管数量已经超过百亿量级。如果没有精准的,功能强大的EDA工具,怎么设计呢?

EDA是芯片设计的必备工具,目前,Synopsys、Cadence和Mentor(Siemens EDA)占据着超过90%以上的市场份额。在10纳米以下的高端芯片设计上,其占有率甚至高达100%。也就是说,现在研发一款10nm以下的芯片,没有以上三家的EDA工具几乎是不可能实现的。

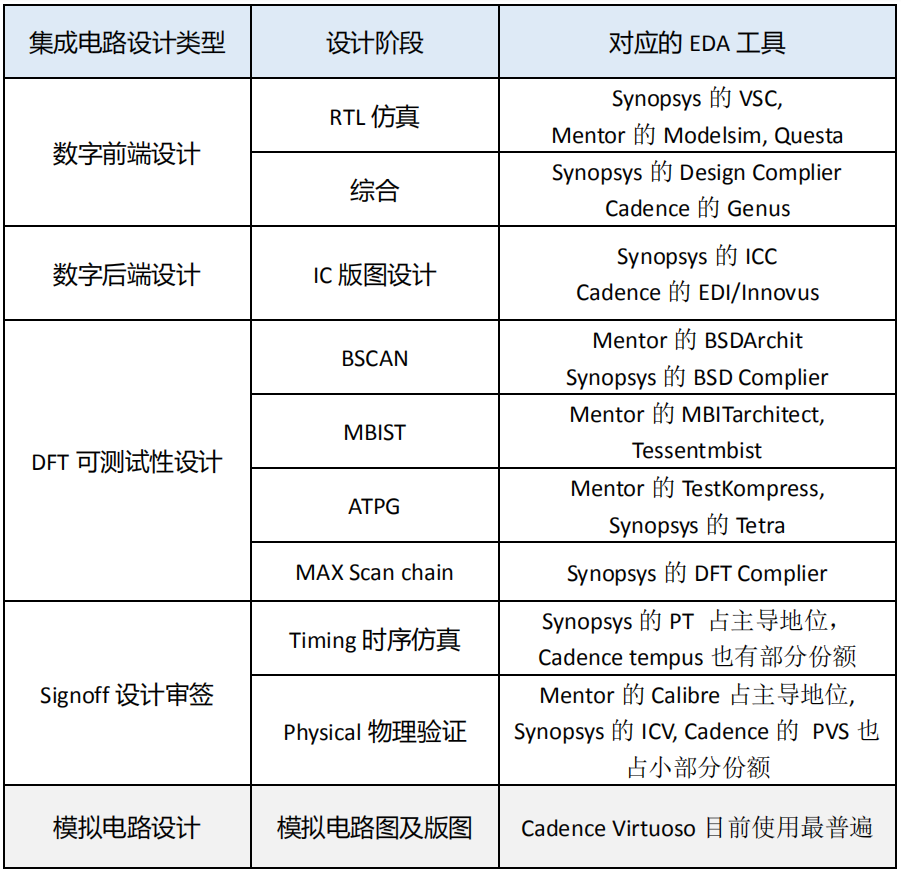

下表所示是目前芯片设计中主流的EDA工具:

芯片设计分为设计、仿真、验证等环节,对应的EDA工具分为设计工具、仿真工具、验证工具等。设计工具解决的是模型的构建,也就是从0到1(从无到有)的问题,仿真和验证工具解决模型的确认,也就是1是1还是0.9或者1.1的问题。因此,从EDA开发的角度,设计工具的开发难度更大。此外,设计规模越大,工艺节点要求越高,EDA工具的开发难度也越大。国产EDA工具目前在一些仿真验证点工具上取得一些成绩,在模拟电路设计方面也初步具备了全流程工具,但在大规模集成电路设计上和三大厂商还有很大的差距,尤其在高端数字芯片设计流程上基本还是空白。

1.2 IP

IP(Intelligent Property)代表着知识产权的意思,在业界是指一种事先定义、经过验证的、可以重复使用,能完成特定功能的模块,IP是构成大规模集成电路的基础单元,SoC甚至可以说是基于IP核的复用技术。IP一般分为硬核、软核和固核。IP硬核一般已经映射到特定工艺,经过芯片制造验证,具有面积和性能可预测的特点,但灵活性较小;IP软核以HDL形式提交,灵活性强,但性能方面具有不可预测性;IP固核通过布局布线或利用通用工艺库,对性能和面积进行了优化,比硬核灵活,比软核在性能和面积上更可预测,是硬核和软核的折中。

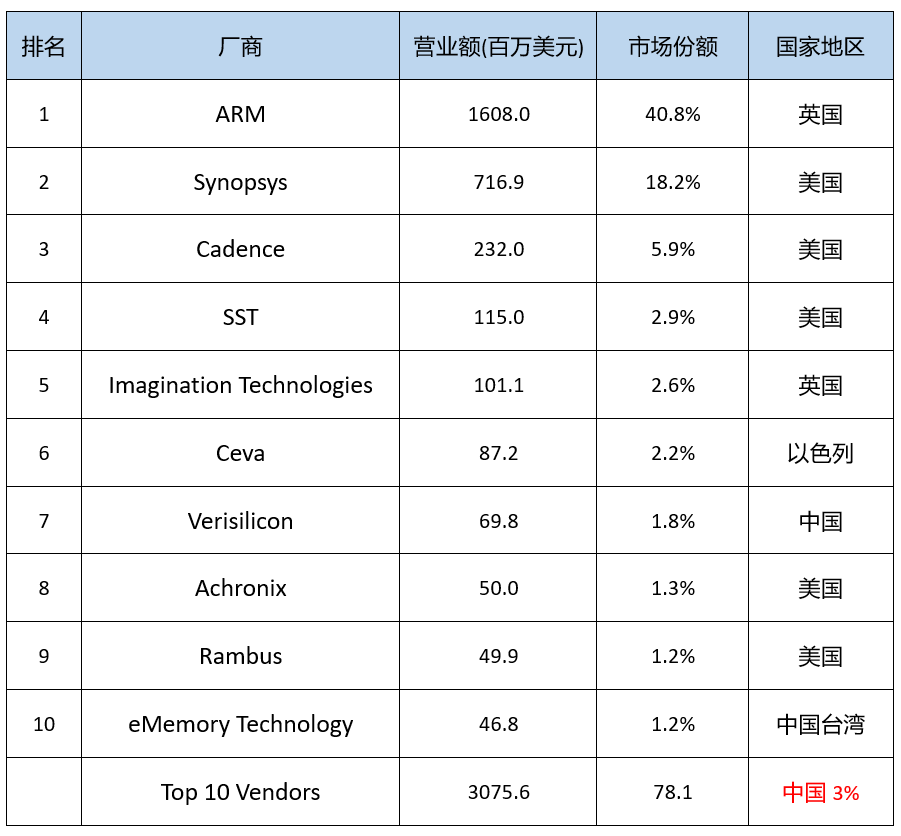

下表为目前全球前10大IP提供商,可以看到中国有两家入围前十,但是两家市场份额加起来也仅有3%,而ARM一家就占据了40%以上的市场份额,美国的企业则占据了30%的市场份额,如果ARM被英伟达收购,基本上IP市场就是美国的天下了。此外我们也发现,全球最大的两家EDA公司Synopsys和Cadence,在IP领域也同样占据的第二、第三的位置。

下图所示为IP的种类,其中处理器占51%,接口IP占22.1%,数字类占8.1%,其他占18.8%,处理器类ARM一家独大,在接口类IP中,Synopsys是业界领导者。

我们需要考虑的是,在设计的芯片中那些IP是自主设计的,那些是外购的,这些外购的IP是否存在不可控因素?如果你设计的SoC仅仅是把别人的IP打包整合,那自主可控性就要大打折扣了。

下面,我们以华为麒麟980为例,了解一下芯片研发中的IP使用情况。

麒麟980芯片集成的主要部件有CPU、GPU(俗称显卡)、ISP(处理拍照数据)、NPU(人工智能引擎)和基带(负责通信)。

根据华为官方资料,ISP是华为自研,NPU是华为和寒武纪合作的成果,至于CPU(Cortex-A76)和GPU(Mali-G76)则是华为向ARM公司购买的授权,包括指令集授权和内核授权。

如果没有IP授权,还有没有可能自研麒麟980芯片,目前看来,没有 。

1.3 设计流程

芯片设计流程通常可分为:数字IC设计流程和模拟IC设计流程。

数字IC设计流程:芯片定义 → 逻辑设计 → 逻辑综合 → 物理设计 → 物理验证 → 版图交付。

芯片定义(Specification)是指根据需求制定芯片的功能和性能指标,完成设计规格文档。

逻辑设计(Logic Design)是指基于硬件描述语言在RTL(Register-Transfer Level)级实现逻辑设计,并通过逻辑验证或者形式验证等验证功能正确。

逻辑综合(Logic Synthesis)是指将RTL转换成特定目标的门级网表,并优化网表延时、面积和功耗。

物理设计(Physical Design)是指将门级网表根据约束布局、布线并最终生成版图的过程,其中又包含:数据导入 → 布局规划 → 单元布局 → 时钟树综合 → 布线。

数据导入是指导入综合后的网表和时序约束的脚本文件,以及代工厂提供的库文件。

布局规划是指在芯片上规划输入/输出单元,宏单元及其他主要模块位置的过程。

单元布局是根据网表和时序约束自动放置标准单元的过程。

时钟树综合是指插入时钟缓冲器,生成时钟网络,最小化时钟延迟和偏差的过程。

布线是指在满足布线层数限制,线宽、线间距等约束条件下,根据电路关系自动连接各个单元的过程。

物理验证(Physical Verificaiton)通常包括版图设计规则检查(DRC),版图原理图一致性检查(LVS)和电气规则检查(ERC)等。

版图交付(Tape Out)是在所有检查和验证都正确无误的前提下,传递版图文件给代工厂生成掩膜图形,并生产芯片。

模拟IC设计流程:芯片定义 → 电路设计 → 版图设计 → 版图验证 → 版图交付。

其中芯片定义和版图交付和数字电路相同,模拟IC在电路设计、版图设计、版图验证和数字电路有所不同。

模拟电路设计是指根据系统需求,设计晶体管级的模拟电路结构,并采用SPICE等仿真工具验证电路的功能和性能。

模拟版图设计是按照设计规则,绘制电路图对应的版图几何图形,并仿真版图的功能和性能。

模拟版图验证是验证版图的工艺规则、电气规则以及版图电路图一致性检查等。

这里,我们做一个简单的总结:

芯片设计:就是在EDA工具的支持下,通过购买IP授权+自主研发(合作开发)的IP,并遵循严格的集成电路设计仿真验证流程,完成芯片设计的整个过程。在这个过程中,EDA、IP、严格的设计流程三者缺一不可。

目前看来,在这三要素中最先可能实现自主可控的就是设计流程了。

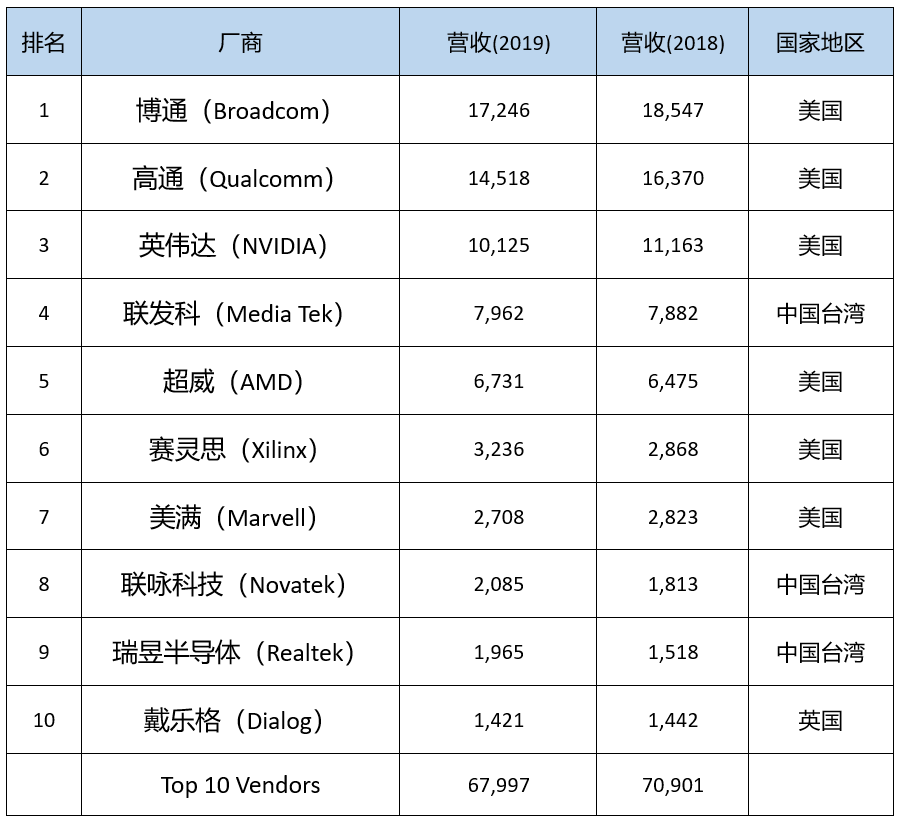

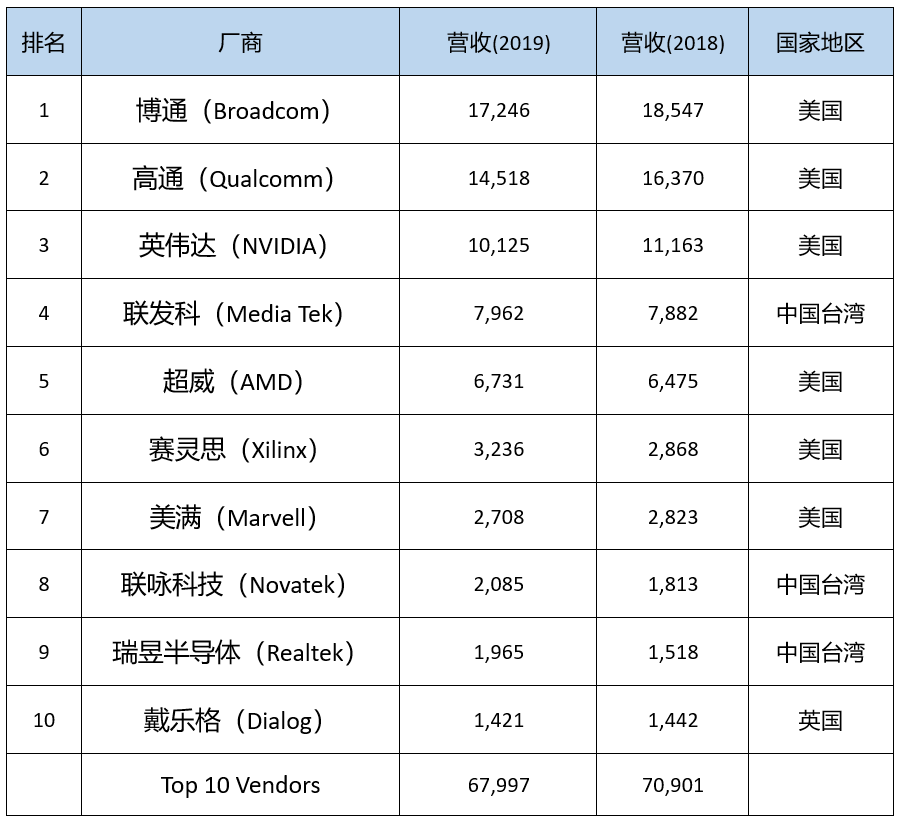

下表列出了当前世界前10的芯片设计公司,供大家参考。

| 上一篇:欧阳明高: 新能源车与革命报告 | 下一篇:让应用性能up up,第三代半导体究竟.. |

安徽省合肥市高新区长宁大道789号5号楼