随着近年来宽禁带功率器件的发展,电力电子系统具有同时实现高效率和高功率密度的潜力。随着对更高驱动功率需求的增加,牵引逆变器中的开关器件对电流能力的要求越来越高。然而,单个芯片的热机械应力限制了芯片上的有效面积。因此,单个SiC MOSFET芯片的电流等级也受到限制。多芯片并联已成为提高电力电子系统电流能力的必然途径。然而,由于不对称的版图、不匹配的器件参数和不同的冷却条件,并联芯片之间的不平衡电流是不可避免的。

不平衡的电流会进一步导致不匹配的功率损耗和不平衡的结温,这意味着并联芯片的退化速率和热机械应力不匹配。那么多芯片电源模块的可靠性和稳定性就可能受到挑战。在实际应用中,为了避免不平衡电流的灾难性破坏,往往会对多芯片功率模块进行降额处理。为了充分利用各并联芯片的容量,提高多芯片功率模块的可靠性,需要抑制多芯片功率模块中并联SiC MOSFET芯片间的电流不平衡。多芯片电源模块中的电流不平衡包括静态电流不平衡和动态电流不平衡。

静态不均流主要指各并联SiC MOSFET在通态时由于输出特性和结温的差异及支路阻抗的不一致,使得负载电流在各并联SiC MOSFET上的分布不均衡;动态不均流主要指各并联SiC MOSFET开通和关断过程开始的时刻以及对应过程中,源电极电流变化速率的不一致致使部分SiC MOSFET承受较大的电流应力。本文首先分析导致静、动态电流不均衡的原理和相关影响因素,再从功率回路、驱动回路两个方面对现存的均流改进方法进行讨论概述。

(一) 静态不均流及其因素:

1、饱和导通压降的影响

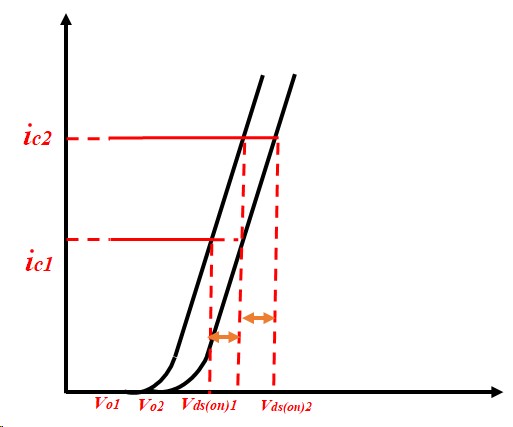

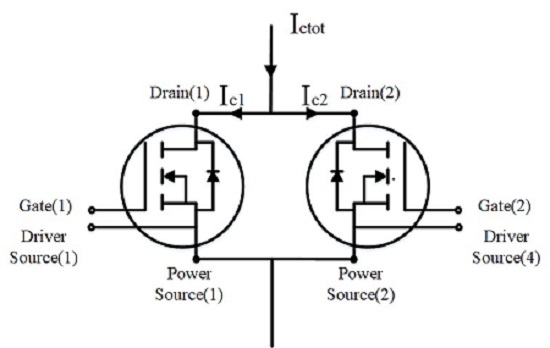

SiC MOSFETs输出特性的饱和压降对静态不均流的影响至关重要,图1为两并联SiC输出特性曲线及其简化等效电路示意。

图1并联SiC MOSFETs的示意图及其输出特性

图1中,VDS(on)1和VDS(on)2分别为两个并联SiC MOSFETs中C1和C2在饱和区下的源极电压,由于饱和压降较低时SiC MOSFETs的输出特性为非线性,而在饱和压降较高时近似呈线性,因此可以得到C1和C2的输出特性。

|

|

(1) |

其中Vo1、Vo2为分别为C1和C2输出特性曲线线性化后与Vds轴的交点,即开启电压;R1和R2分别为C1和C2的通态电阻;IC1和IC2分别为C1和C2的源极电流;ICtot为Q1和Q2的源级电流之和。由于C1和C2为并联关系,存在数学关系:VDS(on)1=VDS(on)2=VDS(on),结合式(1)定义SiC MOSFETs并联时的静态电流不均衡度,即:

|

|

(2) |

选用同一批次的芯片时,芯片之间阈值电压的值相差不大因此Vo1=Vo2=Vo,因此公式(2)可以被简化为

|

|

(3) |

由并联SiC MOSFETs静态均流模型可知, 静态均流的影响因素主要是SiC模块的输出特性, 通过相同的电流,饱和压降Vds(on)越大的模块在并联时分得的电流越少。 输出特性受IGBT模块的栅极电压控制,当增大Vgs时,模块的饱和压降Vds(on)会减小。

2、工作结温影响

|

|

(4) |

Ron为SiC MOSFETs的通态电阻;Rch为沟道电阻、Ra为积累层电阻、Rj为JFET电阻、Repi为外延层电阻。其中,Ra和Rj与器件的制造工艺有关,Repi会随器件结温的升高而略有增大,Rch作为通态电阻,主要受门极导通电压和结温的影响。

|

|

(5) |

式中:L为IGBT的沟道长度;Z为单位面积的沟道宽度;μns为沟道反型层电子的迁移率;Cox为单位面积的栅氧化层电容;VG,on为导通时对应的驱动电压;VGE(th)为IGBT的开通阈值电压。

沟道反型层电子的迁移率μns是关于结温Tj的减函数,即:

|

|

(6) |

随着SiC MOSFETs结温的升高,其通态电阻会增大进而导致其源极电流减小,使得Ron通态电阻较小的SiC MOSFETs流过更多电流。因此受温度的影响,多并联SiC MOSFETs的静态不均流会发生自调节。

(二) 并联SiC MOSFETs并联不均流的主要因素:

动态不均流主要是指并联SiC MOSFETs导通和关断时刻,较先导通或较后关闭的模块会在瞬间流过较大的过电流,如果超过额定负荷范围,就很有可能损毁模块。SiC MOSFETs开通、关断过程起始时刻的不一致通常源于门极驱动信号或门极驱动回路参数的不一致,集电极电流在开通、关断过程中变化速率的不一致则与器件内部参数及门极驱动电压有关。

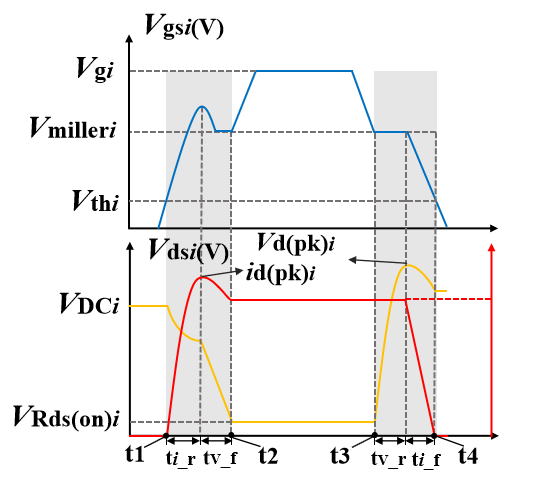

图2给出了SiC MOSFETs的定性开关波形。动态电流不平衡主要发生在阴影区域。在此期间,SiC MOSFETs工作在饱和区。因此,它们可以被建模为由栅源电压( Vgs )控制的电流源。

图2. SiC MOSFETs动态开关波形

被续流二极管钳位的负载电感可以建模为与寄生电容( Cp )并联的电流源。SiC MOSFETs的漏源寄生电容( Cds )可以忽略不计。并且栅源寄生电容( Cgs )和栅漏寄生电容( Cgd )在并联时表现出动态特性。

|

|

(7) |

以SiC MOSFETs的开通过程为例,在该过程中存在开通延迟时间td(on),它对应的SiC MOSFETs门极电压由关断时的稳态值达到导通阀值所经过的时间

|

|

(8) |

RG,on和Rint分别为门极驱动电阻和SiC内部的门极电阻;Ciss为SiC的结电容;VG,on和VG,off分别为门极驱动电路开通和关断时输出的稳态电压;Vth为SiC的导通阀值电压。门极驱动电阻及输出电压、SiC内部的门极电阻SiC结电容以及导通阀值电压的差异都会对并联SiC开通过程起始时刻的一致性产生一定影响,此外,开通延迟时间td(on)还会随着结温Tj的升高而增大。

在图2阴影部分工作的区域为饱和电流区对应的电为

|

|

(9) |

因此在饱和区的电流变化速率为:

|

|

(10) |

Id为漏极电流;Vgs为门极电压;gm为等效跨导,与SiC自身参数以及门极电压有关,可知其对动态均流存在影响。

与开通过程类似,SiC的关断过程也与上述参数存在一定关联。SiC自身参数以及门极驱动电压都会对并联SiC的开关过程起始时刻和电流变化速率的一致性产生影响。另外,对于单个SiC模块,其内部布局(如引入开尔文发射极)会影响各并联芯片的电流均衡回,这意味着包括SiC在内的功率模块内部需要更加合理的布局以确保并联芯片间电流的均衡分布。

多并联SiC MOSFETs不均流影响因素

|

影响因素 |

动态电流 |

稳态电流 |

|

|

芯片参数 |

阈值电压 |

★★ |

◯ |

|

跨导 |

★★ |

◯ |

|

|

导通电阻 |

◯ |

★★★ |

|

|

寄生电容 |

★ |

◯ |

|

|

功率回路参数 |

漏极寄生电感 |

◯ |

★ |

|

源级寄生电感 |

★★★ |

★ |

|

|

漏极寄生电容 |

◯ |

★★ |

|

|

漏极寄生电阻 |

◯ |

★★ |

|

|

公共支路阻抗耦合 |

★★ |

★★ |

|

|

互感耦合 |

★★ |

★ |

|

|

驱动回路参数 |

栅源级电压 |

★★ |

◯ |

|

驱动信号延迟 |

★★ |

◯ |

|

|

驱动电阻 |

★★ |

◯ |

|

|

栅极寄生电感 |

◯ |

◯ |

|

注:★表示各类影响因素在相同差异度下对电流分配的影响程度,★越多影响程度越大,◯表示对电流分配无影响或影响可忽略。

二、解决不均流问题的研究现状:

现有的改善均流的方案主要有4类:器件预筛选法、有源栅极驱动法、版图优化法和无源元件法。

1.器件预筛选法:在很多情况下,并联器件之间的电流不平衡是由器件的电气参数不匹配引起的。在并联器件的开关瞬态过程中,各器件的阈值电压极大地影响了器件间的均流。因此,在使用并联器件搭建电路或模块时,通常会对器件进行预筛选,使Vth离散度保持在可接受的范围内。

2.主动栅极控制法:对并联器件的电流进行检测,然后调整栅极延时和/或ON态栅极电压来平衡电流。在并联SiC MOSFET的情况下,由于SiC MOSFET的快速开关速度,使用主动方法来平衡电流变得越来越具有挑战性。

3.无源器件法:在某些情况下,增加无源元件以改善均流效果。最常用的无源方法是在每个器件的栅极添加电阻。

4.版图优化法:在使用SiC MOSFET的应用中,由于开关速度较高,均流对功率回路的寄生电感非常敏感。然而,当并联的开关数量高于两个时,要实现完美的对称布局是非常困难的。

[1]肖雅伟,唐云宇,刘秦维,等.并联IGBT模块静动态均流方法研究门电源学报,2015,13(2):64-70

[2]C. Zhao, L. Wang, F. Zhang, and F. Yang, “A method to balance dynamic current of paralleled SiC MOSFETs with Kelvin connection based on response surface model and nonlinear optimization,” IEEE Trans. Power Electron., vol. 36, no. 2, pp. 2068–2079, Feb. 2021.

[3]穆峰,刘宜鑫,李鑫,等.IGBT并联应用均流控制技术综述[J].电源学报,2024,22(01):119-132.

[4]王小红,李世存,梁帅奇,等.IGBT并联关键技术和测试方法的研究[J]电力电子技术,2014,48(10):45-47.

[5]王雪松,赵争鸣,袁立强,等.应用于大容量变换器的IGBT并联技术[J] 电工技术学报,2012,27(10):155-162.

| 上一篇:栅极电荷理解与应用 | 下一篇:一、SiC MOSFET非钳位电感(UIS)测试.. |

安徽省合肥市高新区长宁大道789号5号楼