一、SiC MOSFET非钳位电感(UIS)测试与重复可靠性退化机制

(一)非钳位电感测试

非钳位电感测试是一种用于评估功率器件(如SiC MOSFET)在高应力瞬态条件下性能的重要手段。此测试模拟了器件在高压和高功率瞬态条件下的实际工作情况,重点考察其抗击穿能力、热稳定性及能量耗散能力。

1、测试电路及原理

(1)测试电路的组成

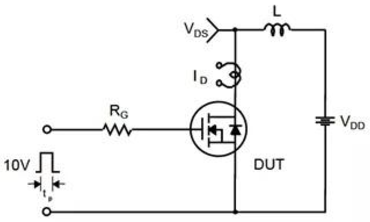

图1. UIS测试电路的基本电路结构

非钳位电感测试电路设计的核心在于实现器件在关断瞬间承受电感释放的能量,电路通常由以下部分组成:

•直流电源 :提供稳定的直流电压,用于为电感充电。

:提供稳定的直流电压,用于为电感充电。

•待测器件 :被测功率MOSFET,通过导通和关断操作实现电感能量释放的控制。

:被测功率MOSFET,通过导通和关断操作实现电感能量释放的控制。

•电感 :储存能量并在MOSFET关断瞬间释放,形成高压尖峰,是测试的关键元件。

:储存能量并在MOSFET关断瞬间释放,形成高压尖峰,是测试的关键元件。

•续流二极管 :在电感释放能量时提供续流通路,保护电路的其余部分。

:在电感释放能量时提供续流通路,保护电路的其余部分。

•驱动电路:控制MOSFET的导通和关断,测试过程中需精准触发关断瞬间的测试。

(2)测试电路的原理及波形

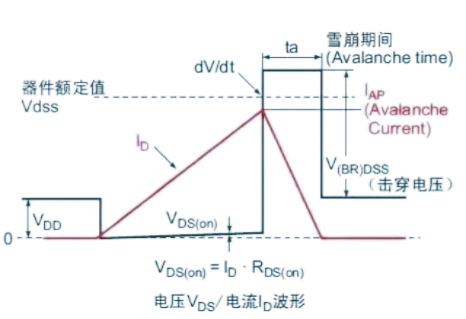

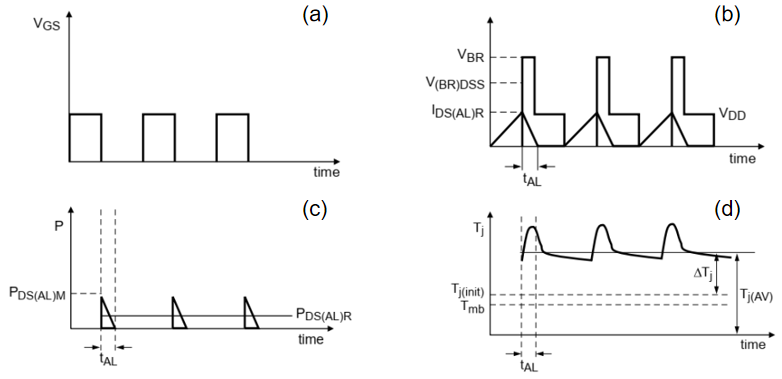

UIS测试的完整时序波形图如图2所示,包含三个主要阶段。

•第一阶段:电感储能

首先是电感储能阶段,器件栅极由低电平切换至高电平(通常为10~15V),器件由关断→导通,在器件导通阶段,电感电流逐渐上升,表现为器件漏源电流的逐渐增大,直到电感电流增大至雪崩电流IAP。在MOSFET导通时,电源通过电感充电,电流以线性方式增加,公式为:

其中, 为电源电压,L为电感值,t为导通时间。

为电源电压,L为电感值,t为导通时间。

•第二阶段:电压尖峰形成

然后是电压尖峰形成的阶段,由于此时电感的电感电流只有一条泄放路径,电感能量的瞬时释放会驱使器件进入雪崩状态,器件两端的电压迅速上升,器件的击穿电压将超过额定电压。MOSFET在关断瞬间,由于电感电流不能瞬时消失,电感释放的能量通过续流二极管和DUT形成高电压尖峰,尖峰电压可由以下公式估算:

其中, 是电流下降的变化率,

是电流下降的变化率, 为续流二极管的正向压降。

为续流二极管的正向压降。

•第三阶段:能量耗散

最后是能量耗散阶段,雪崩状态将持续约几十μs的时间,直至电感释放的能量以热的形式被DUT吸收或通过续流二极管耗散完毕。总能量可以表示为:

为MOSFET关断前的电感电流峰值。

为MOSFET关断前的电感电流峰值。

图2. UIS测试的基本波形

(二)SiC MOSFET器件雪崩效应及重复UIS可靠性退化机制

1、SiC MOSFET的雪崩效应

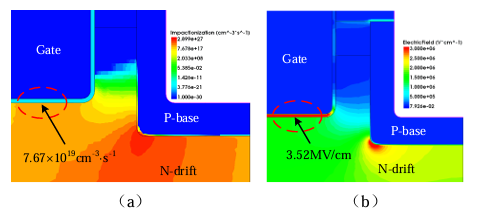

图3. SiC MOSFET在UIS过程中的 (a)碰撞电离率分布 (b)电场分布[1]

如图3所示,SiC MOSFET在发生雪崩时,碰撞电离率最高的区域集中在PN结的尖峰位置,这与电场的分布相对应。同时,碰撞电离率较高的位置还集中在栅氧层的下方,在栅氧层下方区域内形成了一个雪崩电离的集中区域。

在雪崩击穿过程中,通过碰撞电离产生的载流子在强电场作用下不断加速。当这些载流子获得足够的能量后,形成高能态载流子并越过栅氧化层与漂移区之间的势垒,注入到栅氧化层中。这一过程会导致栅氧化层内的缺陷密度逐步增加。随着雪崩击穿的反复发生,栅氧化层内的缺陷逐渐累积。当缺陷密度达到一定程度时,栅氧化层内可能形成导电路径,从而引发器件的栅漏短路失效。

2、SiC MOSFET在UIS过程中的退化机制

(1)MOSFET的单次雪崩退化机制

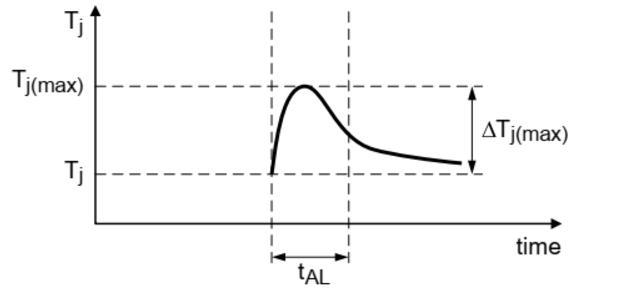

MOSFET的单次雪崩事件的失效机理是由于结点温度超过了最大温度限值,持续的时间一般在μs量级。在这种情况下,MOSFET会产生灾难性的损坏。如下图中,如由雪崩事件导致的瞬时温度超过了推荐的限值,热量不足以传递到芯片引线框和封装体,器件的风险增高。为了达到最佳的稳定性,这里的限值是由最大温度降额而来。

对于单次雪崩测试来说,我们希望测定到器件的极限雪崩能量,因此我们通过改变电感值以及电感在第一阶段充电的峰值电流,改变雪崩的峰值能量直至达到器件的雪崩极限。

图4. 雪崩过程中的器件结温

(2)MOSFET的重复雪崩退化机制

单次雪崩事件就是器件在应用中由于错误的条件导致出现雪崩事件,例如电器过载。电路应用中是没有预先为这类雪崩做预防设计的。

重复雪崩是指电路应用中雪崩式MOSFET的预期工作模式。这里说的雪崩式设计的性能,而且不依赖于雪崩事件发生的次数。

图5. 重复UIS过程中的(a)VGS-t (b)VDS-t和IDS-t (c)PDS-t (d)结温变化

大多数厂商都避免提供与功率MOSFET重复雪崩能力有关的数据。这主要是由于这种工作情况的复杂性和以及识别此种工况下元器件物理衰减过程的难度而决定的。由于雪崩事件具有创伤的性质,重复雪崩工作可能会是对MOSFET有害的。即使出现了一个低于单次UIS限值的个别雪崩事件也是有害的。另外,这种工作引入了额外的参数,如频率,占空比和雪崩事件中的热阻抗。所以在评估MOSFET的重复雪崩性能时,一般会取60%或80%的极限雪崩能量作为每次雪崩的能量,同时对电感和电流控制变量,从而调整每次雪崩的能量大小。

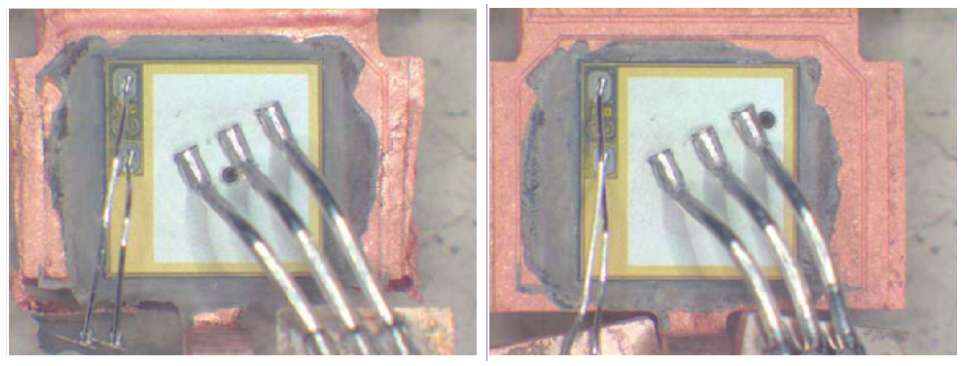

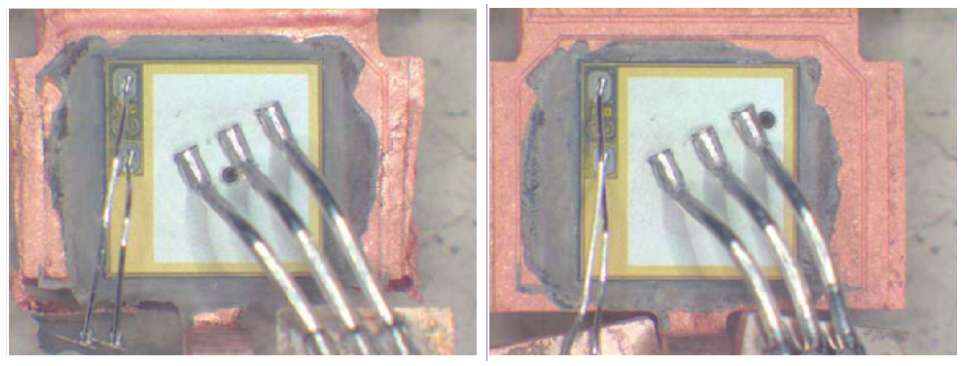

如果雪崩事件的持续时间在毫秒级(ms),通常会在晶圆中央——即电流密度最大的位置——出现烧毁痕迹。这是由于连接引线与晶圆结合部的电流密度较高,导致该区域易于失效。然而,由于散热片的存在,失效点往往不会出现在引线连接点的正下方,而是发生在晶圆温度最高的区域。

对于微秒级(μs)的短暂雪崩事件,烧毁位点可能分布于整个晶圆的任意位置。这种情况下,电流在器件内部难以集中,同时事件时间较短,器件自热效应不足,导致温升分布较为均匀。即使是更短的雪崩事件,由于晶圆边缘单元的结构不连续性,烧毁现象可能集中出现在晶圆的角部区域。

图6. 重复雪崩应力下器件失效的位点示例:ms级(左),μs级(右)

(三)总结

本文简要介绍了SiC MOSFET非钳位电感测试的电路原理及其对应的器件物理机制,定量分析了器件在测试过程中的电路参数和波形参数。进一步地,从芯片结构和封装的角度分别说明了SiC MOSFET的可靠性机制,旨在帮助读者更全面地了解SiC MOSFET非钳位电感测试的整体流程、原理和失效表现,以便对SiC MOSFET的可靠性筛选和可靠性优化有更深入认识。

(四)参考文献

[1]高崇兵.SiC基功率MOSFET器件UIS应力及短路退化机理研究[D].电子科技大学,2024.DOI:10.27005/d.cnki.gdzku.2024.001253.

[2]贺鹏.1200V高可靠性SiC MOSFET器件特性研究[D].电子科技大学,2023.DOI:10.27005/d.cnki.gdzku.2023.003307.