近年来,随着宽禁带功率器件技术的不断进步,电力电子系统在提升效率与功率密度方面呈现出巨大的发展潜力。面对电动汽车牵引逆变器、工业驱动等高功率应用场景对电流输出能力需求的持续增长,采用多芯片并联结构已成为扩展SiC MOSFET模块电流容量的主流技术路径。然而,在实际并联运行过程中,由于布局不对称、器件参数分散性以及散热条件不均等因素,各芯片之间难以实现理想的动态均流,尤其在开关瞬态过程中表现出明显的电流分布不平衡。

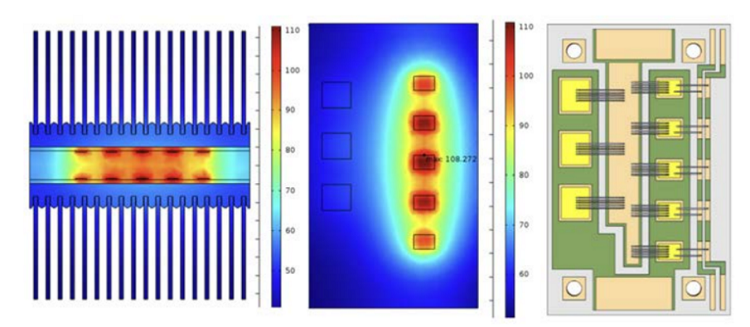

图1.常规布局布线设计的 SiC 功率模块中并联芯片结温分布

动态电流不平衡问题主要表现为并联的各个SiC MOSFET在开通和关断过程中电流变化率(di/dt)存在差异,导致部分器件承受较高的瞬时电流应力。这种电流不对称不仅引起开关损耗分布不均,还会造成局部结温升高,加速器件退化,从而制约整个功率模块的可靠性与使用寿命。现有改善动态均流的策略多集中于优化驱动电阻、调整栅极驱动时序、匹配器件静态参数以及优化功率回路布局以降低寄生参数差异等方面。然而,大多数传统动态均流模型存在一个共同局限,即未充分考虑并联支路间互感耦合效应的影响。实际上,在高频开关过程中,相邻导体中变化电流所产生的磁场会相互耦合,进而影响各支路的等效电感,改变电流上升与下降过程的对称性。忽略这一效应,可能导致对动态均流性能评估偏差,甚至在高di/dt工况下引发严重的电流振荡和应力集中。

针对该问题,本研究建立了一个计及互感耦合效应的动态均流评估模型,旨在更全面准确地刻画多芯片并联结构在高频开关过程中的电流分布特性。该模型通过集成交叉耦合电感参数,深入分析磁场相互作用对瞬态电流轨迹的影响,为理解与预测实际运行中的动态不均流现象提供了理论依据。在此基础上,可为进一步的均流优化设计——如合理规划芯片布局、优化母排结构与驱动控制策略——提供支持,从而提升多芯片SiC功率模块的整体性能与可靠性。

(一) 影响动态电流均衡的主要因素

(a)

(b)

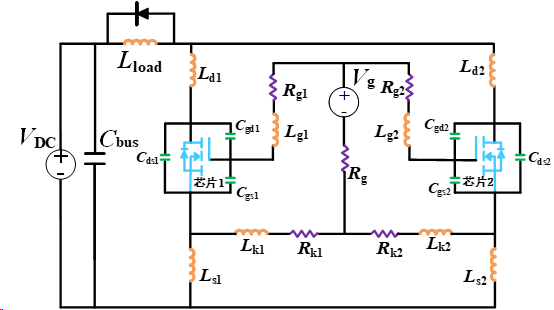

图 2 两并联SiC MOSFET的电路图 (a) 寄生电路模型 (b) 等效动态电路模型

动态不均流主要是指并联SiC MOSFETs导通和关断时刻,较先导通或较后关闭的模块会在瞬间流过较大的过电流,如果超过额定负荷范围,就很有可能损毁模块。SiC MOSFETs开通、关断过程起始时刻的不一致通常源于门极驱动信号或门极驱动回路参数的不一致,集电极电流在开通、关断过程中变化速率的不一致则与器件内部参数及门极驱动电压有关。在整个开通关断过程中,两个并联SiC MOSFET芯片的等效电路如图 2 (a)所示。图中 Ld为漏极寄生电感,Rg为驱动电阻,Lg为驱动电感,Lk为开尔文源极电感,Ls为源极寄生电感,VDC为母线电,Lload为电感,Vg为驱动电源。已有研究表面,并联SiC MOSFET芯片的栅源寄生电容(Cgs)、漏源寄生电容(Cds)以及栅漏寄生电容(Cgd)之间的参数分散性较小,其差异通常可忽略不计。此外,在SiC MOSFET的开关瞬态过程中,器件尚未完全开通,Vds大于栅极电压vgs与阈值电压Vth的差值,此时SiC MOSFET工作于饱和区。在该工作区中,分析重点为沟道电流,Cds能够被忽略不计。Cgd和Cgs可视为动态并联,共同构成等效输入电容(Ciss),其表达式如公式(1)所示。因此,图2(a)中的芯片1和芯片2可简化为由栅源电压控制的等效电流源模型,如图2(b)所示。

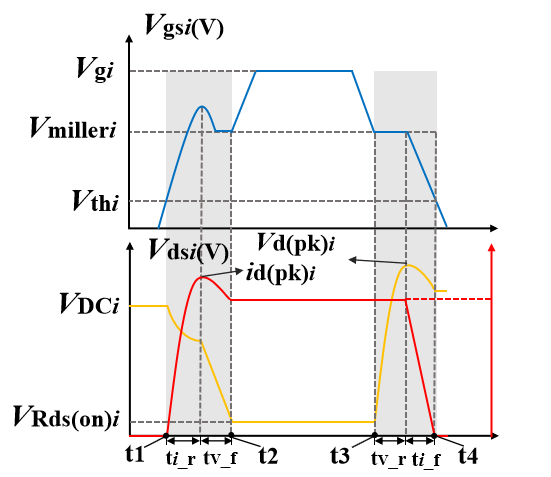

图3给出了SiC MOSFETs的定性开关波形。动态电流不平衡主要发生在阴影区域。在此期间,SiC MOSFETs工作在饱和区。因此,它们可以被建模为由栅源电压( Vgs )控制的电流源。

图3. SiC MOSFETs动态开关波形

在图1阴影部分工作的区域为饱和电流区对应的电为

因此在饱和区的电流变化速率为:

因此在饱和区的电流变化速率为:

Id为漏极电流;Vgs为门极电压;gm为等效跨导,与SiC自身参数以及门极电压有关,可知其对动态均流存在影响。

根据之前文献[1]的描述,有几个因素可能导致当前的不平衡。两个MOSFET之间的电流差可以表达为:

式中,∆id表示两个并联芯片之间的动态电流峰值差异,∆Lg、∆Lk、∆Ls分别是栅极寄生电感、开尔文源寄生电感和源极电感的差。GTg、GTk、GTs和GTV是受电路参数和MOSFET特性影响的系数。方程(2-3)表明,所有∆Lg、∆Lk、∆Ls和∆Vth都可能导致动态电流不平衡。相应的系数GTg、GTk、GTs和GTV表示电感差对电流不平衡的影响。此外,由于驱动回路中的电流(ig, ik)明显小于功率回路中的电流,因此可以合理地忽略它们的影响。因此,与GTs相比,影响因子GTg和GTk变得可以忽略不计。根据[2]中的推导,∆Ls的影响在动态均流中占主导地位。

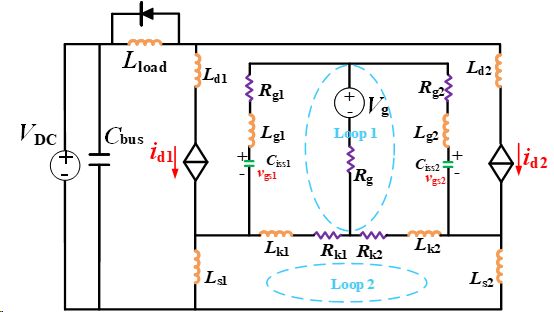

(二) 基于耦合互感效应的动态电流影响

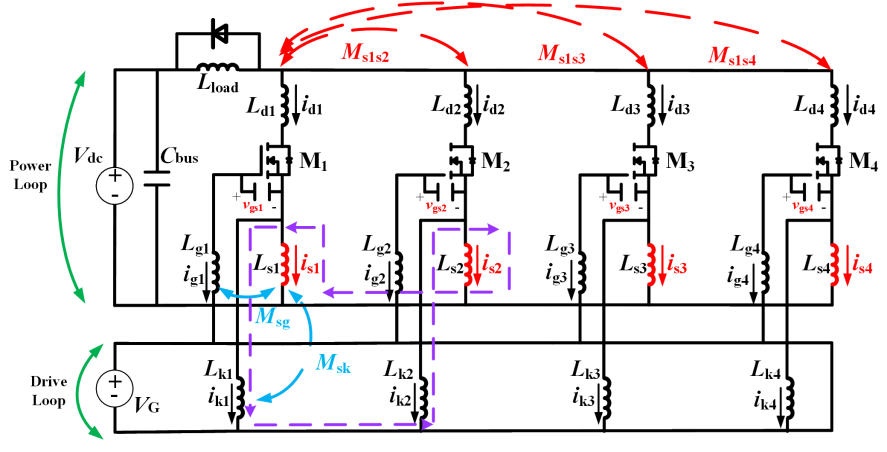

寄生电感对功率器件的开关特性具有重要影响。因此,本文建立了一个考虑不同电流段自感与互感耦合的动态耦合寄生电路模型,如图4所示。在该电路模型中,Lx 和 Mx 分别表示不同电流段的简化自感值与互感值。具体而言,Ldx、Lsx、Lgx 和 Lksx 分别表示漏极、源极、栅极和开尔文源极的自感;Msxsy、Msxgy 和 Msxky 则分别表示不同源极之间、源极与栅极之间,以及源极与开尔文源极之间的互感。

图4. 四并联芯片的动态电流寄生电路模型

根据电感的定义与电磁感应定律,电感 Ls1, Ls2, Ls3的源级电压能被表达为vs1, vs2 , and vs3

在饱和区内,四个并联SiC MOSFET的漏极电流可近似表示为:

因此 ∆idxy 在 Mx 和 My 能被推到为:

根据公式 (7), 当 ∆vgsxy=0 , 动态电流能实现平衡.

根据 Kirchhoff's Voltage Law (KVL), 驱动电路中有

∆vgs 能被写为

应用 Kirchhoff's Voltage Law (KVL) 到图2中规定紫色回路有

代入 (10) into (9), 能被重新写为

当 ig is 忽略时, (11) 能被写为

假设并联平衡实现, ∆vgs 满足下列公式:

源级电压在(12)中能满足

动态电流能满足以下形式

此时自感和互感应该满足以下条件

公式(16)提出了一个明确的动态电流优化准则,为后续实现更精确的动态均流控制奠定了理论基础。该准则通过量化关键参数对瞬态电流分布的影响,为电路设计、布局优化以及驱动策略的调整提供了可遵循的理论依据与评价标准,对提升多芯片并联系统的可靠性与综合性能具有重要指导意义。

[1] X. Liu et al., “Analytical and Optimal Strategy of Dynamic Current Balancing for Paralleled SiC MOSFETs with Cu-Clip Interconnection Considering Mutual Coupled Inductances,” IEEE Trans. Compon. Packag. Manuf. Technol., pp. 1–1, 2025.

[2] C. Zhao, L. Wang, and F. Zhang, “Effect of asymmetric layout and unequal junction temperature on current sharing of paralleled SiC MOSFETs with kelvin-source connection,” IEEE Trans. Power Electron., vol. 35, no. 7, pp. 7392–7404, Jul. 2020.

| 上一篇:逆导型RC-IGBT设计简介及优化方向 | 下一篇:功率模块结温测试:核心意义与技术挑.. |

安徽省合肥市高新区长宁大道789号5号楼