功率器件作为光伏、新能源汽车、工业控制等的核心控制元器件,其可靠性越来越受到重视。然而,由于行业对性能的极限追求,以及响应国家能源降本政策而成本压缩需求,芯片的小尺寸化成本竞争的核心动力,为此各芯片供应商不断在缩小芯片尺寸上做深入研究,减小终端尺寸为一主流趋势,过小的终端尺寸导致表面电场的不断增加,逐渐暴露出终端的可靠性问题。

一、器件结构

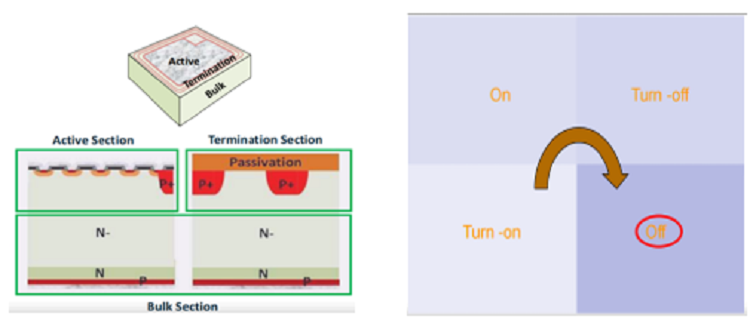

完整的功率器件结构主要由三部分组成,分别为有源区(active)、终端(termination)及硅体区(bulk),如图1所示。在实际应用中,器件会经历开通、导通、关断及阻断四个工作模式,在阻断状态下,有源区近似于一个平面结,但在有源区边缘由于柱面和球面结的存在导致耗尽层在边缘内陷,从而造成电场集中,击穿电压下降,终端区的作用就是将此处的耗尽层尽可能向芯片边缘延展,避免电场的过分集中,从而避免击穿电压的下降。

图1 功率器件结构及工作模式

二、对结终端的主要要求

1. 功率器件的阻断能力不能简单的评价为静态反向偏置下的阻断能力,还需要保证在整个特定要求的温度范围内开关动作时依然有好的阻断能力,比如开关动作时抑制动态雪崩及较低的电压过冲。

2. 高温热稳态下,终端能表现出较低的漏电流。随着业界对功率器件越来越高的工作结温要求,功率器件必须满足相应的可靠性要求,较低的漏电流无疑是必要要求。

3. 在严酷的工作及环境条件下,终端需具备可靠的阻断行为。

目前常见平面结终端设计包括保护环GR、结终端扩展JTE及横向变掺杂VLD。在低成本及严苛的性能要求下,器件设计者都在尽可能的压缩终端尺寸,这导致更高的表面电场,较高的电绝缘失效及非密封封装下的外界干扰等。因此,结终端需要更好的钝化及保护,以提高整个生命周期的可靠性。

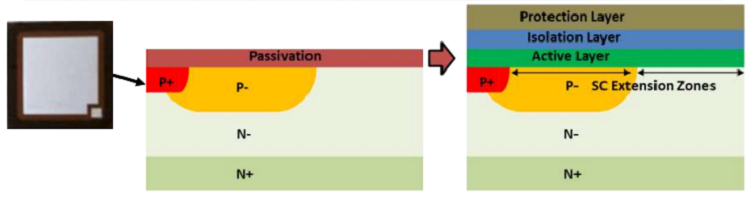

较好的钝化层应具备控制、绝缘及保护结终端的能力,所以终端层应包含如图2所示的紧邻硅表面的有源层Active Layer,上层的绝缘层isolation layer及顶层的保护层。

图2 钝化结构组成

有源层与硅形成了界面,其工艺影响了硅表面电荷Qss,该层包含二氧化硅、场板及半绝缘层SIPOS,它们通常被用来帮助进一步延展阻断状态下的耗尽层,而半绝缘层SIPOS可以额外为电荷提供泄放途径。

上层绝缘层及顶部保护层具备较高的绝缘能力及较强的保护能力,确保不会因表面电弧导致提前电压击穿,以及保护终端免遭外部机械破坏或污染。

三、表面电荷Qss

功率器件为追求更好的性能,芯片厚度略来越薄,为保证耐压需求,越来越多的采用较高的衬底电阻率,即衬底掺杂浓度变低,而不是增加芯片厚度和增加终端尺寸。

表面电荷Qss通常带正点,会在硅表面感应出电子,导致耗尽层在硅表面向内凹陷,而不是所期盼的向外延展,如图3所示。对采用低衬底掺杂的功率器件,表面电荷Qss的影响相对更为明显。

图3 表面电荷对耗尽层扩展的影响

四、SIPOS终端结构及作用机理

半绝缘多晶硅SIPOS不是纯净的多晶硅,也不是完美的二氧化硅,它是在LPCVD过程中,通过向硅烷SiH4中同时掺入N2O而沉积的一种非晶硅薄膜,其中均匀分布着氧原子。

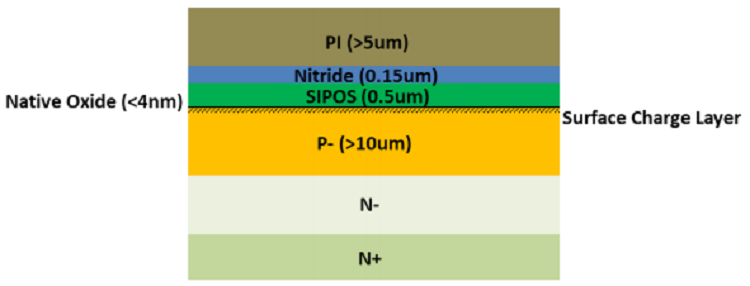

(一) SIPOS终端结构

SIPOS可以理解为氧掺杂的多晶硅,其电阻率通常在通常10⁸ Ω·cm左右,其结构如图4所示,硅表面通常为小于4nm的自然氧化层,SIPOS厚度通常在500nm左右,其内含氧量通常在20-30%之间,SIPOS对湿气比较敏感,所以其上需要氮化硅的保护,顶部则采用聚酰亚胺钝化保护。

图4 SIPOS终端结构

(二) SIPOS薄膜作用

1. 电荷中和效应:SIPOS具有很高的电阻率,非完美的绝缘体,在电场的作用下,薄膜中会产生微弱的导电电流。当硅表面因表面电荷(正电荷)存在电势时,SIPOS膜作为一高阻路径,允许电荷重新再分布,这种缓慢的电荷传输有效中和了表面电荷的影响。

然而,在不同电压和温度下,其支配的传导机制也不同。在低电场和低温下,硅的体传导起主导作用。在高压下,更多的载流子能进入SIPOS薄膜,SIPOS传导相对体传导起主导作用,如图5所示。

图5 SIPOS终端漏电流

2. 均匀表面电场:当施加高电压时,SIPOS膜自身的电阻会形成一个电阻分压器,使SIPOS膜表面的电势从高电位到低电位线性的、连续的下降,而不是突变。这种电势线性分布迫使下方的硅表面的电场变得均匀,消除电场峰值。

3. 物理阻挡和钝化作用:SIPOS膜本身可作为一个物理屏障,阻挡外部的可动离子直接到达敏感的Si-SiO2界面。SIPOS通常直接淀积在硅上,但其与硅的界面态密度可以通过工艺优化来控制。在很多结构中,会先有一层薄的热氧化层,然后再淀积SIPOS。SIPOS在这里主要起到电场控制和电荷中和作用,而薄的热氧化层则提供良好的界面钝化。

五、总结

SIPOS薄膜通常与JTE或VLD终端结合使用,这两种终端表面掺杂浓度较低,对电荷敏感性较高,SIPOS薄膜的应用能极大提高其可靠性。SIPOS的难点在于工艺控制,其需要再电荷控制与漏电流之间做出平衡。由于其复杂的表面机理及传导特性,SIPOS钝化依然是一个很难理解的工艺技术。但比较明确的是,SIPOS的厚度、含O2量必须严格控制,界面氧化层其重要作用,其必须尽可能控制的非常薄。需要优化SIPOS退火工艺确保均匀膜层并致密,以及可控的界面电荷。

| 上一篇:光储用三电平拓扑(INPC/TNPC/ANPC.. | 下一篇:一、 晶圆减薄工艺-Taiko工艺介绍 |

安徽省合肥市高新区长宁大道789号5号楼