一、 引言

作为现代电力电子系统的核心开关器件,IGBT高效管理着能量的流动,同时也时刻面临最为严峻的挑战——短路故障。这种异常状态可在数微秒内引发能量的急剧聚集,严重危及整个系统的安全。究其根本,IGBT的短路失效模式大多都可归为热失效:局部热量在芯片内迅速积累,导致温度超越材料极限,从而造成期间损毁。因此,提升芯片短路耐量,本质上是一场与热量和时间的极限赛跑。本文将系统解析IGBT芯片级短路耐量设计的物理原理,揭示这道关乎电力电子系统可靠运行的“安全防线”的内在机制。

二、 芯片级短路耐量设计方法

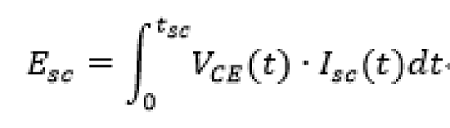

短路能量的积累,决定着芯片能否安全关断。该能量可通过短路期间电流与电压乘积的积分来计算。在这场与时间和热量的赛跑中,设计师的核心目标明确:在规定的测试电压和短路耐受时间(通常为几微秒至十微秒)内,尽可能减少积累在芯片内部的总能量。

因此,一个最直接且有效的设计思路是:在短路故障发生时,设法降低IGBT的短路饱和电流Isc。更小的电流意味着更低的瞬时功率与更少的总热能沉积,从而为芯片在熔毁温度前实现“安全关断”提供宝贵的时间

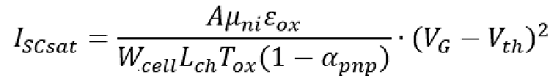

那么,如何从芯片设计层面精准地控制这个关键的短路饱和电流呢?其核心可由退饱和电流ISCsat的物理公式揭示:

其中,A为芯片参与导电的元胞区域的面积;μni为MOS沟道中电子的迁移率;εox为栅极氧化层的介电常数;Wcell为元胞宽度;Lch为沟道长度;Tox为栅极氧化层厚度;αpnp为寄生PNP晶体管电流放大系数;VG为施加的栅极-发射极电压;Vth为栅极阈值电压。在芯片基本架构和技术代系确定后,设计者主要通过以下两个关键途径来有效调整短路耐量:工艺调整提升Vth与结构设计合理的A的面积与形状。

1、 工艺优化——提升阈值电压Vth

Vth是IGBT导通的“门槛电压”,由于短路饱和电流与(VG-Vth)的平方成正比,因此提升Vth是抑制短路电流强有力的手段之一。通过调整沟道区的掺杂浓度等关键工艺参数,可以精准提升Vth。例如,在典型15V栅极驱动下,将Vth从5V提升至6V,就能使短路电流降低约20%,为芯片关断赢得关键时间。然而,这亦是一把双刃剑,过高的Vth会直接导致器件在正常工作时导通压降与开通能量增加,带来更大的稳态损耗和发热。因此,设计的精髓在于在短路安全性与运行效率之间,找到最佳平衡点。

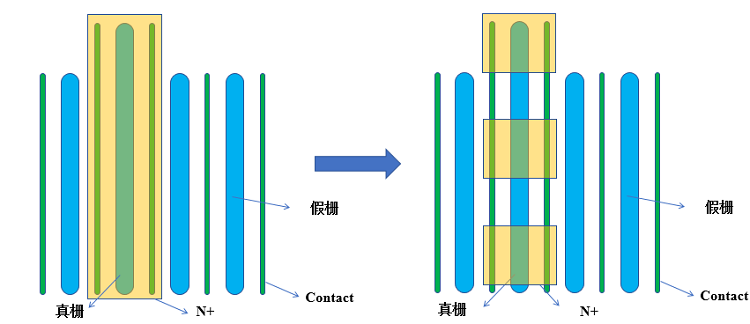

2、 结构优化——减小发射极注入面积A

这是从芯片物理结构入手的根本性方法,其核心在于控制元胞中N+发射极的尺寸与布局。在IGBT芯片内部,N+发射极区是电子注入的源头,通过巧妙的版图设计(例如采用真假栅交替、间隔NPS注入的图案形状),可以有效减小该区域的有效注入面积。这种设计在不显著影响正常导通特性的前提下,显著降低短路饱和电流,提升器件固有的抗短路能力。如今,先进的微图案化和精细光刻技术,使得这种微米尺度的几何控制成为可能。

三、 结语

综上所述,提升IGBT的短路耐量,绝非依靠单一参数的调整,而是一场贯穿工艺、结构与系统的精密协同,是在器件物理、芯片制造与版图设计三个维度上寻求最优解的系统工程。我们深入探讨的物理公式,正是串联这些维度、指导设计决策的核心理论工具。理解每一个参数,就掌握了平衡IGBT安全性、效率与成本的关键。如今,随着新能源汽车、工业控制、可再生能源等领域对功率密度与可靠性提出近乎苛刻的要求,IGBT的短路鲁棒性已成为衡量其性能的关键指标。每一次技术的迭代,都在向着更安全、更高效、更耐用的目标迈进。

| 上一篇:SiC MOSFET体二极管震荡全解析:从.. | 下一篇:IGBT器件氢注入与磷注入 |

安徽省合肥市高新区长宁大道789号5号楼